# Axxia<sup>®</sup> AXX2500 Family of Communication Processors

Virtual Pipeline<sup>™</sup> Technology and Accelerator Engines Reference Manual

Advance, Version 0.1 September 2012

DB13-000407-00

AXX2500 Virtual Pipeline Technology and Accelerator Engines Reference Manual September 2012

## **Revision History**

| Version and Date            | Description of Changes |

|-----------------------------|------------------------|

| Version 0.1, September 2012 | Initial Release        |

LSI, the LSI & Design logo, Axxia, and Virtual Pipeline are trademarks or registered trademarks of LSI Corporation or its subsidiaries. PowerPC is a registered trademark of International Business Machines Corp. All other brand and product names may be trademarks of their respective companies.

This advance document describes a product in design or under development and contains information that may change substantially for any final commercial release of the product. LSI Corporation makes no express or implied representation or warranty as to the accuracy, quality, or completeness of information contained in this document, and neither the release of this document nor any information included in it obligates LSI Corporation to continue development or to make a commercial release of the product. LSI Corporation reserves the right to make changes to the product(s) or information included to in to obligates LSI Corporation to continue development or to make a commercial release of the application or use of any product or service described herein, except as expressly agreed to in writing by LSI Corporation, nor does the purchase, lease, or use of a product or service from LSI Corporation convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Corporation or of third parties. LSI products are not intended for use in life-support appliances, devices, or systems. Use of any LSI product in such applications without written consent of the appropriate LSI officer is prohibited.

This document contains proprietary information of LSI Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of LSI Corporation.

| Corporate Headquarters | Email                 | Website     |

|------------------------|-----------------------|-------------|

| Milpitas, CA           | globalsupport@lsi.com | www.lsi.com |

| 800-372-2447           |                       |             |

Document Number: DB13-000407-00 Copyright © 2012 LSI Corporation All Rights Reserved

# **Table of Contents**

| Chapter 1: Introduction to the Axxia Virtual Pipeline Technology         |    |

|--------------------------------------------------------------------------|----|

| Overview                                                                 | 9  |

| Accelerator Engines                                                      |    |

| Engine Sequences and Virtual Pipeline Instances                          |    |

| Branching Virtual Pipeline Instances and Flows                           |    |

| APIs for Managing Virtual Pipeline Instances                             |    |

| Task Communication                                                       | 14 |

| Messaging in Pipelines                                                   |    |

| Passing Parameters Using Tasks                                           |    |

| Task Management                                                          |    |

| Maintaining Task Order                                                   |    |

| Flow Parameters.                                                         |    |

| Backpressure                                                             |    |

| Backpressure Signals                                                     |    |

| Namespaces.                                                              |    |

| •                                                                        |    |

| Engine Tables<br>Namespace Configuration                                 |    |

| Namespace with More than One Engine Table                                |    |

| Engine Table Entry Size and Memory Usage                                 |    |

| Managing Namespaces and Engine Tables from FPL Software or Using the RTE |    |

| Sharing Data Between Engine Tables                                       |    |

| Engine Table Memory Addressing                                           |    |

| Engine Table Code Generation                                             |    |

| Troubleshooting                                                          |    |

| Engine Monitoring<br>Task Monitoring                                     |    |

| Conditional Logging                                                      |    |

|                                                                          |    |

| Chapter 2: Modular Packet Processor (MPP) Engine                         | 33 |

| Overview                                                                 |    |

| MPP Classification Capabilities                                          |    |

| Features                                                                 |    |

| Pattern Processing Subengines                                            |    |

| Hash Subengine                                                           |    |

| State Subengine                                                          |    |

| Prequeue Modifier                                                        |    |

| Semaphore Subengine                                                      |    |

| MPP Packet Integrity Check Subengine                                     |    |

| MPP and Engine Sequence Interaction                                      |    |

| MPP Block Diagram                                                        |    |

| MPP Pattern Processing Engines.                                          |    |

| MPP Hash Engine                                                          |    |

| MPP Prequeue Modifier (PQM)                                              |    |

| MPP Semaphore Subengine                                                  |    |

| MPP Packet Integrity Check Subengine                                     |    |

| Input and Output Parameters                               |    |

|-----------------------------------------------------------|----|

| MPP End Engine Input Task Parameters                      |    |

| MPP Start Engine Output Task Parameters                   |    |

| Packet Processing                                         |    |

| Classification                                            |    |

| Dynamic Resource Management                               |    |

| Names, Timers, and Hash Table Structure                   |    |

| Stateful Processing                                       |    |

| Packet Modification                                       |    |

| MPP Interaction with Engine Sequences                     |    |

| FPL Flow and Tree Instruction Fetch                       |    |

| Task Debugging                                            |    |

| Exception Handling                                        |    |

| State Engine                                              |    |

| MPP Packet Integrity Check Engine                         |    |

| Hash Engine                                               |    |

| MPP System Monitoring Capabilities                        |    |

| MPP Task Debugging                                        |    |

| Chapter 3: Memory Management Block (MMB) Engine           |    |

| Overview                                                  |    |

| Features.                                                 |    |

|                                                           |    |

| Chapter 4: Packet Assembly Block (PAB) Engine             |    |

| Overview                                                  |    |

| Features                                                  |    |

| PAB Functions                                             |    |

| Identifying the Segment Data for Reassembly               |    |

| Defining the Segment Placement in the Reassembly Context. |    |

| Defining the Reassembled Packet Data to be Transmitted    | 55 |

| Transmitting the Reassembled Packet                       |    |

| Discarding the Reassembly Context                         |    |

| Checking Reassembly Context Status                        |    |

| Using the PAB                                             |    |

| Creating a Reassembly Context.                            |    |

| Adding Segments to Reassembly Contexts                    |    |

| Transmitting All or Part of a Reassembled Packet.         |    |

| Clearing a Reassembly Context                             |    |

| Bypassing the PAB                                         |    |

| Using Bit-level Operations.                               |    |

| Using Timers with the PAB                                 |    |

| Using Sequence Numbers                                    |    |

| PAB Configuration Overview                                |    |

| PAB Task Receive Queue Configuration                      |    |

| PAB Task Input Parameters.                                |    |

| PAB Task Output Parameters                                |    |

| PAB Task Output Parameters without the GetStatus command  |    |

| PAB Task Output Parameters with the GetStatus command     |    |

|                                                           |    |

| PAB Commands                                                     | 64 |

|------------------------------------------------------------------|----|

| Independent PAB Command Parameters                               |    |

| Using the Engueue Commands                                       |    |

| Using the Transmit Commands                                      |    |

| TransmitCopy Command                                             |    |

| Transmit with Discard Command                                    |    |

| Discard Command                                                  |    |

| Sticky Discard Command.                                          |    |

| Cleanup Command                                                  |    |

| Passthrough Command                                              |    |

| GetStatus_reasmState Command                                     |    |

| GetStatus_reasmPrioMem Command                                   |    |

| GetStatus_PrioMem Command                                        |    |

| PAB Exception Handling                                           |    |

| Hardware Exception Handling                                      |    |

| Error Containment                                                |    |

| PAB Performance Monitoring Facilities                            |    |

| -                                                                |    |

| Chapter 5: Modular Traffic Manager (MTM) Engine                  |    |

| Overview                                                         | 78 |

| Features                                                         |    |

| Buffer Management                                                |    |

| Traffic Scheduling and Traffic Shaping                           |    |

| Flow Control.                                                    |    |

| Multicast Support                                                |    |

| MTM Processing                                                   |    |

| MTM Functional Description                                       |    |

| Scheduling Packets                                               | 80 |

| Root Scheduler                                                   |    |

| Adjusting Packet Size                                            |    |

| Arbitration and Scheduling Modes                                 |    |

| Rate Shaping Traffic                                             |    |

| Scheduler Operation                                              |    |

| SDWRR Scheduling                                                 |    |

| DWRR Scheduling                                                  |    |

| Strict Priority Scheduling                                       |    |

| Controlling Arbitration with Scripts                             |    |

| Applying and Receiving Backpressure                              |    |

| Defining Buffer Management Policies                              |    |

| Building the Scheduling Hierarchy                                |    |

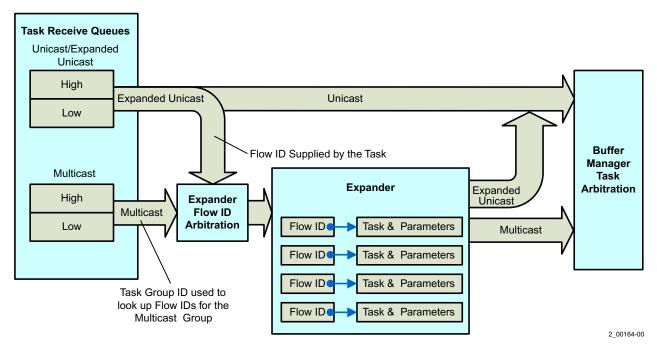

| MTM Task Receive Queues and Buffer Management                    |    |

| -                                                                |    |

| Task Receive Queues                                              |    |

| MTM and Expander Engines                                         |    |

| Task Arrival and Enqueuing Arbitration                           |    |

| Queue, Scheduler, and Global Parameters                          |    |

| Buffer Management<br>Draining Traffic from Queues and Schedulers |    |

| -                                                                |    |

| MTM Input and Output Parameters                                  |    |

| MTM Input Parameters                                             |    |

| MTM Output Parameters                                            |    |

| Setting the Final Output Target                                  |    |

| Unicast Processing                                               |    |

|     | Expander Input and Output Parameters                                                                             | 94   |

|-----|------------------------------------------------------------------------------------------------------------------|------|

|     | Expander Input Parameters                                                                                        | . 94 |

|     | Expander Output Parameters                                                                                       |      |

|     | Expanded Unicast Processing                                                                                      |      |

|     | Multicast Processing                                                                                             |      |

|     | MTM Exception Handling                                                                                           |      |

|     | MTM Performance Monitoring Facilities                                                                            | 96   |

|     | oter 6: Timer Manager (TMGR) Engine                                                                              |      |

|     | Overview                                                                                                         | 97   |

|     | Features                                                                                                         | 97   |

|     | Time Representations                                                                                             | 97   |

|     | Formats                                                                                                          |      |

|     | Axxia Time                                                                                                       |      |

|     | Axxia Delta Time                                                                                                 |      |

|     | Axxia Compressed Absolute Time                                                                                   |      |

|     | Accuracy and Precision for Axxia Time                                                                            |      |

|     |                                                                                                                  |      |

|     | Non-cancellable Timers                                                                                           |      |

|     | Using the TMGR Engine                                                                                            |      |

|     | Characteristics                                                                                                  |      |

|     | Task Input Queue Configuration.                                                                                  |      |

|     | Starting TMGR Processing                                                                                         |      |

|     | Task Input Parameters                                                                                            |      |

|     | Task Output Parameters                                                                                           |      |

|     | Exception Handling                                                                                               |      |

|     | External Timing Reference Interface                                                                              |      |

|     | Performance Monitoring Facilities                                                                                | 102  |

|     | Timer Support                                                                                                    |      |

|     | Timer Support for Resource Management                                                                            |      |

|     | Timer Support for Scheduling                                                                                     |      |

|     |                                                                                                                  |      |

|     | Support for External Clock Generation and Synchronization.                                                       |      |

|     | Generating an Output Reference Clock from Axxia Time<br>Using an Input Reference Clock to Synchronize Axxia Time |      |

|     | Mapping an Input Strobe to Synchronize Axxia Time with an External Device                                        |      |

|     | Using an Output Strobe to Synchronize Axxia Time with an External Device                                         |      |

|     | Support of Timing over Packet (ToP) Protocols                                                                    |      |

|     | Using EIOA Engines to Capture Network Time from Packets                                                          | 104  |

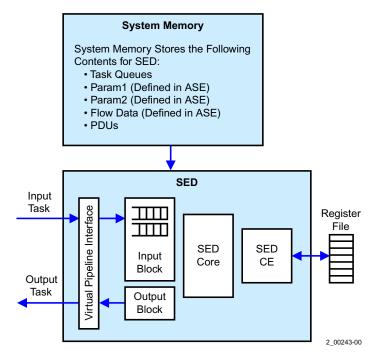

| Cha | oter 7: Stream Editor (SED) Engine                                                                               | 106  |

|     | Overview                                                                                                         |      |

|     | Features                                                                                                         |      |

|     | SED Architecture                                                                                                 |      |

|     | SED Task Receive Queue Configuration                                                                             |      |

|     | SED Functional Description                                                                                       |      |

|     | SED Capabilities                                                                                                 |      |

|     | SED Packet Editing Parameters                                                                                    |      |

|     | SED Parameter Processing                                                                                         |      |

|     | SED Input and Output Parameters                                                                                  | 109  |

|     | SED Input Parameters                                                                                             |      |

|     | SED Output Parameters                                                                                            | 110  |

| SED Parameter Structure                                              | 110 |

|----------------------------------------------------------------------|-----|

| Parameter Data Structure                                             | 110 |

| Parm1 and Parm2 Namespace Table Parameters                           | 110 |

| Indirect Mode Characteristics                                        |     |

| Merging Script Parameters                                            |     |

| Using Parm1 and Parm2 Parameter Combinations<br>Using SED Parameters |     |

| Exception Handling.                                                  |     |

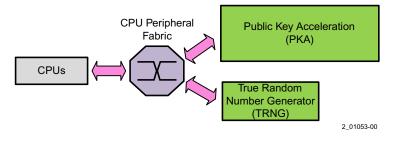

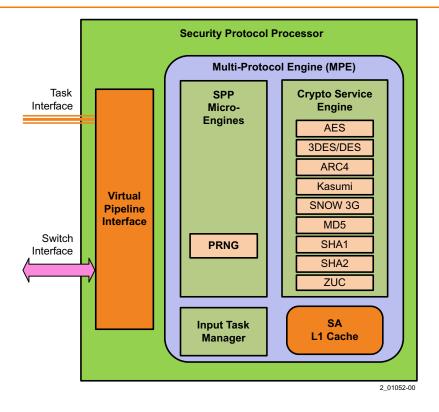

| Chapter 8: Security Protocol Processor (SPP) Engine                  | 115 |

| Overview                                                             |     |

| Supported Protocols and Features                                     |     |

| Configuring Secure Connections                                       |     |

| SPP Architecture.                                                    |     |

| Virtual Pipeline Model                                               |     |

| SPP Virtual Pipeline Operation                                       |     |

|                                                                      |     |

| Chapter 9: Deep Packet Inspection (DPI) Engine                       | 120 |

| Overview                                                             | 120 |

| DPI Features                                                         | 120 |

| Internal Architecture                                                | 120 |

| Compiling Rulesets to Configure the DPI                              | 122 |

| DPI Task Input Queue Configuration                                   | 122 |

| Context Across Packets Within a Flow                                 |     |

| Initiating DPI Processing                                            |     |

| DPI Task Input Format                                                |     |

| Load Balancing                                                       |     |

| Result Format                                                        |     |

| Start Conditions                                                     | 126 |

| Maximum Output                                                       | 126 |

| DPI Task Output Format                                               | 127 |

| FirstResult and AllResult Formats                                    |     |

| Vector Result Format                                                 |     |

| DPI Data Structures, Commands, and Exception Handling.               | 129 |

| Chapter 10: Packet Integrity Check (PIC) Engine                      | 130 |

| Overview                                                             | 130 |

| Features                                                             | 130 |

| CRC and Checksum Operations.                                         |     |

| Supported IP Layer 4 Protocols                                       |     |

| PIC Engine Processing                                                |     |

| PIC Input and Output Parameters                                      | 133 |

| PIC Input Parameters.                                                |     |

| Setting Input Parameters.                                            |     |

| PIC Output Parameters<br>PIC Status Parameter                        |     |

| PIC Exception Handling                                               |     |

| PIC Exception Handling                                               |     |

|                                                                      |     |

| Chapter 11: Network Compute Adapter (NCA)                            | 138 |

| Overview                                                             | 138 |

| Chapter 12: Ethernet Input Output Adapter (EIOA) Engines           | . 139 |

|--------------------------------------------------------------------|-------|

| Overview                                                           | . 139 |

| EIOA Engines with Preclassifier and Ethernet Switch (PCX) Features | . 139 |

| -<br>Hardware-based Address Learning                               |       |

| VLAN Support                                                       |       |

| Access Control List Support                                        |       |

| Ingress Policing                                                   |       |

| Scheduling and Shaping                                             |       |

| Axxia ElOA Architecture.                                           |       |

| EIOA Packet Classification                                         |       |

| Virtual Pipeline Destinations                                      |       |

| Egress Processing                                                  |       |

| Ingress Packet Data Flow Overview                                  | . 144 |

| EIOA Core Logic Processing                                         | . 144 |

| Ingress Packet Processor (IPP) Functions                           | . 144 |

| Bridging Layer Classification and Switching.                       | . 145 |

| Building the Bridging Lookup Keys                                  | . 145 |

| MAC Address Learning                                               |       |

| MAC Address Aging.                                                 |       |

| ACL Classification                                                 |       |

| Ingress Policing.                                                  |       |

| Destination Result Map and Mask Operations                         |       |

| EIOA Multicast Replication                                         | . 150 |

| VLAN Statistics                                                    | . 150 |

| EIOA Egress Processing and Scheduling                              | . 151 |

| Queue Scheduling                                                   |       |

| Port Shaping                                                       |       |

| Packet Field Modification                                          |       |

| Backpressure Support                                               |       |

| Handling PAUSE Frames                                              |       |

| Engine Backpressure                                                |       |

| Use Case Examples                                                  |       |

| Preclassifier MPP Assist                                           |       |

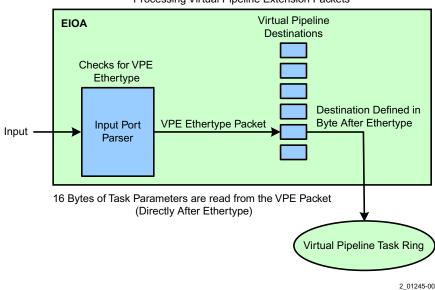

| Virtual Pipeline Extension (VPE)                                   |       |

| Simple QoS without using the MTM                                   |       |

|                                                                    |       |

| Axxia Communication Processor Glossary                             | . 155 |

# **Chapter 1: Introduction to the Axxia Virtual Pipeline Technology**

This chapter introduces the LSI® Axxia® Virtual Pipeline™ technology. Additional information about specific engines is available in their respective chapters.

## **Overview**

The Axxia architecture lets you use both dedicated accelerator engines and general purpose processors in any sequence to process packets. The processing does not require the CPU for scheduling or packet processing. This approach enables system designers to create multiple, custom packet processing paths to match their application packet and traffic flow processing requirements. This removes the need for special CPU programming to control job queuing and scheduling for each packet processing path.

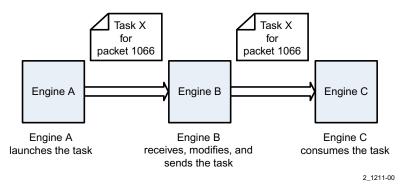

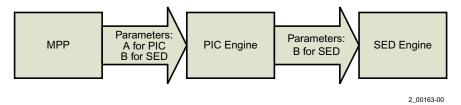

System designers can use the Axxia architecture to design packet processing paths with a sequence of accelerator engines that can receive a packet processing request, perform processing, and then send the packet to another engine for additional processing. The following figure shows an example Virtual Pipeline instance, which is a sequence of accelerator engines.

#### Figure 1 Example Accelerator Engine Sequence (Simple Virtual Pipeline Instance)

A set of engines that define a processing path through the device is called an *engine sequence*. One or more engine sequences can make up a *Simple Virtual Pipeline instance*. You can have multiple independent engine sequences (similar to the previous figure) or dependent engine sequences in a *Branching Virtual Pipeline instance* that accomplish the packet processing.

To create a system, the designer identifies the processing steps required for each traffic flow, and builds sequences of engines to provide the appropriate processing in the required order. The Virtual Pipelines define one or more custom processing engine sequences through the Axxia device.

Engines within an engine sequence, communicate by passing a message or *task* from one engine to the next sequential engine. A task is a data structure that passes information from engine to engine to process a packet. Accelerator engines can create, consume, or modify tasks.

Tasks passed through an engines sequence, contain the following general information.

- Contain a packet, or more often, have pointers to packet data in memory.

- Contain parameters that instruct engines how to process the packet.

Accelerator engines can perform prioritize tasks using these operations.

- Assign a priority (task created by start engines)

- Place tasks into select queues, based on priority

- Adjust task priority based on queue congestion (backpressure)

When a packet arrives for processing, the engine that receives the packet creates a task for that packet. Processing engines use the task to exchange packet processing information. The task contains processing parameters passed from engine to engine in the Virtual Pipeline instance. The task parameters affect packet processing for each engine. When an engine completes its processing for a task, it sends the task to the next engine in the Virtual Pipeline instance.

You can use Virtual Pipeline instances to provide the entire engine-to-engine processing path for the packet, and also for coprocessing with the CPUs. When used for coprocessing, Virtual Pipeline instances define simple engine paths to and from the CPUs, allowing the CPUs to offload compute-intensive packet processing functions to the accelerator engines. For example, the main packet processing can be done by the CPUs, using the accelerator engines to perform encryption, decryption, reassembly, or scheduling as steps in the CPU processing.

## **Accelerator Engines**

The Axxia architecture lets you configure dedicated accelerator engines and general purpose processors in any sequence to process packets. The Axxia device includes the following accelerator engines.

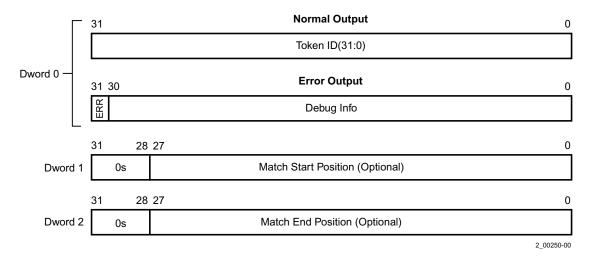

## Ethernet Input and Output Adapters (EIOA), Preclassifier and Ethernet Switch (PCX)

Each EIOA engine can receive packets from and transmits packets to external Ethernet interfaces. You can configure and monitor the Ethernet interfaces, plus the preclassification and switching (PCX) logic. The Axxia device can preclassify and switch traffic between Ethernet ports, which offloads this processing from the intermediate engines.

There are two EIOA adapters in the AXX2500 device, EIOA0 and EIOA1.

The EIOA engine serves as a start engine or an end engine for an engine sequence, creating a new task on packet arrival, and receiving a task for transmitting a processed packet.

## Modular Packet Processor (MPP)

The MPP engine classifies packets using highly multithreaded pattern processing engines which provide the required processing and access items such as routing tables and access control lists. You can program the MPP engine using the Functional Programming Language (FPL).

Based on the classification, the MPP engine (using the FPL) can perform the following additional packet processing.

- Maintaining multiple hash tables for dynamic flow classification.

- Maintaining statistics and policing traffic flows.

- Editing packets, including segmenting packets, adding headers or footers, and duplicating, adding, modifying, or deleting packet data.

- Performing CRC and checksum operations.

The MPP engine serves as a start engine or end engine for engine sequences.

## Packet Assembly Block (PAB)

The PAB engine performs both traditional reassembly functions and generalized packet data buffering for simple segment-level editing and transmission.

The PAB engine is command driven, with commands sent to the PAB as tasks from another accelerator engine such as the MPP engine or the CPU to establish and control reassemblies.

You can use the PAB engine to reassemble packet segments in a sequence that is contiguous, has gaps, or has overlaps, with segments sent later overwriting all or part of previous segments. Gaps can be filled with pad data. For example, you can change both the packet start and endpoints to delete header or trailer information. The PAB engine can accept byte-level and bit-level offsets.

The PAB engine is an intermediate engine in engine sequences.

## Packet Integrity Check (PIC)

The PIC engine calculates a cyclic redundancy check (CRC) or checksum value for a packet. The calculated CRC or checksum value can verify an incoming packet, or calculate a new value for a modified packet. Optionally, the PIC engine can write the calculated CRC or checksum value into the packet.

The PIC engine is an intermediate engine in engine sequences.

#### Stream Editor (SED)

The SED engine is a programmable block editor for packets. For many applications, the SED is an efficient way to modify, update, or add header information. It permits you to edit a packet — header, payload, and trailer — in 128-byte blocks.

The SED engine is an intermediate engine in engine sequences.

#### Modular Traffic Manager (MTM)

The MTM engine performs packet buffer management and scheduling. You can program buffer management policies.

You can configure scheduling structure hierarchy and shaping and scheduling services, with support for weighted, shaped, and strict priority algorithms, with the option to add custom programmed scheduling and custom programmed buffer management. The MTM engine supports up to six levels of scheduling.

The MTM engine is an intermediate engine in engine sequences.

#### Security Protocol Processing (SPP)

The SPP engine accelerates the decryption and encryption of packets for many standard security protocols. It performs packet integrity authentication, anti-replay protection, and programmable security protocol processing that includes packet modifications and error checking.

The SPP engine is an intermediate engine in engine sequences.

#### Deep Packet Inspection (DPI)

The DPI engine performs unanchored searches across one or more packets using standard regular expressions. Based on regular expression search technology, the DPI engine supports simultaneous evaluation of up to one million expressions.

The DPI engine is an intermediate engine in engine sequences.

#### Timer Manager (TMGR)

The TMGR engine provides large-scale (millions) timer services to the CPUs and accelerator engines. The TMGR engine supports timers for the following general purposes.

- Scheduling timer that expires after a set time.

- Time-out timer that prompts for an action.

- Process expiration timer that indicates a process is dead or has timed-out.

The TMGR engine is an intermediate engine in engine sequences.

#### Memory Management Block (MMB)

The MMB engine responds to request from accelerator engines to allocate and de-allocate memory blocks. The MMB engine manages data blocks in memory requested by the other engines. The MMB allocates the data blocks, tracks the number of memory block accesses, and frees the memory when the block contents are no longer needed.

Because accelerator engines use the MMB engine implicitly, you *do not use* this engine as part of an engine sequence.

#### Network Compute Adapter (NCA)

The Network Compute Adapter (NCA) transfers tasks between CPUs (internal or external) and the accelerator engines. The NCA enables the host CPU to configure the all aspects of Virtual Pipeline instances and engine sequences. The NCA can be a start engine or an end engine in an engine sequence.

## **Engine Sequences and Virtual Pipeline Instances**

A set of engines that define a processing path through the device is called an engine sequence.

An engine sequence can include three types of engines. Engines that can serve as the first or last engine in an engine sequence are called start engines or end engines, depending on their location in the sequence. Intermediate engines receive a task, optionally modify it, and send it to the next engine in the sequence.

Sequences optionally include one or more intermediate engines that receive, optionally modify and send the task to next engine. Sequences complete with an end engine that receives and consumes the task.

Engines used in an engine sequence have the following characteristics.

- Start engines create and launch new tasks for packet processing.

- Intermediate engines do not generate new tasks and typically do not consume a received task.

- End engines consume the task.

- Multiple instances of the same intermediate engine type can exist.

- Some engines can be used as the start engine *and* the end engine.

The purpose of an engine sequence is to process tasks (and their associated packets). You can create an engine sequence with two or more engines. Engine sequence processing begins with a task launch by the first engine in the sequence, and concludes with the last engine in the sequence consuming that task. Each task is typically associated with a packet, although there can be tasks without packets.

One or more engine sequences can make up a Virtual Pipeline instance. There are two types of Virtual Pipeline instances.

- Simple Virtual Pipeline instances that contain only one engine sequence.

- Branching Virtual Pipeline instances having two or more branches (engine sequences), that share the same start engine. The start engine selects an engine sequence and sends a task down the selected engine sequence.

## **Branching Virtual Pipeline Instances and Flows**

In some cases, packets from the same source require a different processing path. For example, packets for a traffic flow might contain both unencrypted and encrypted packets. The engine sequences required for both types are identical, except for the addition of the Security Protocol Processor for the encrypted packet path.

Although you can design separate Simple Virtual Pipeline instances for the two cases, this approach duplicates the common software processing to handle common packet operations.

The Axxia architecture provides a branching pipeline option that enables you to launch both cases using the same function from the same start engine.

A Branching Virtual Pipeline instance defines two or more engine sequences, or branches, that share the same starting engine, can use the same set of start engine output parameters, and are grouped together. The start engine for a branching pipeline must be either the MPP, Expander, or CPU.

A user-defined set of packets that require the same type of processing is called a *flow*. To define a specific set of processing parameters for each flow in a pipeline, you can define a flow table. You can use application software to create the flow table. In the table, you use a programmable flow ID as an index to a set of parameter values that are organized as a flow table entry. The start engine for the pipeline loads the flow table values into the task.

**NOTE** When the flow table is updated, any tasks already started, continue to use the original information that existed at the time the tasks started.

The Branching Virtual Pipeline instance launches in the start engine the same way that a single pipeline launches. The start engine determines the appropriate branch for processing the packet based on information that is stored in a separate data structure called a flow table, which the engine references using a flow ID.

A user-defined set of packets that require the same type of processing is called a *flow*. Flows are defined based on some field or data in the packet, such as the source IP address. Each entry in a flow table contains parameters and other information needed to process the packets in that flow. Packets with one set of flow IDs are routed down one branch of the Virtual Pipeline instance, while packets with other flow IDs are routed differently.

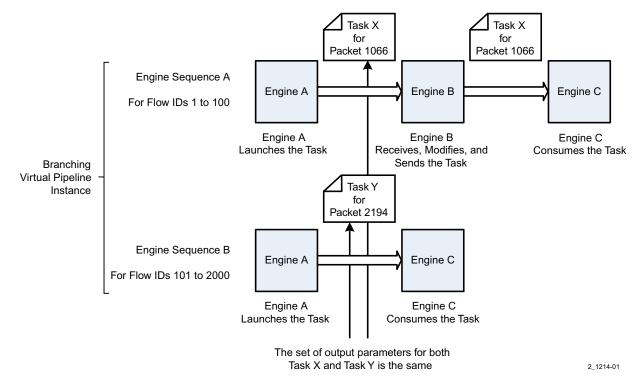

The following figure shows a branching pipeline with two engine sequences.

#### Figure 2 Example Branching Virtual Pipeline Instance

Branching Virtual Pipeline instances are used primarily when the downstream processing in each branch requires a similar set of parameters from the start engine such that the differences between the branches are manageable simply as different entries in the flow table.

## **APIs for Managing Virtual Pipeline Instances**

The run-time environment (RTE) is a set of functions and commands that can initialize, define, and control an Axxia device. The RTE APIs for managing Virtual Pipeline instances at runtime include the following functions.

- ncp\_vp\_handle\_get Get the Virtual Pipeline instance handle given the type of launching engine (CPU, MPP, EIOA and Expander) and the name of the Virtual Pipeline instance

- ncp\_vp\_id\_get Get the Virtual Pipeline id from its instance handle

- ncp\_vp\_num\_flows\_get Get the number of flows defined for a Virtual Pipeline instance

- ncp\_vp\_launch\_engine\_check Determine if a Virtual Pipeline instance is launched by the specified launch engine

- ncp\_vp\_flow\_data\_func\_set Set encode and decode functions for a given engine sequence identified by vpHdl and engineSeqld. The encode function is used by ncp\_vp\_flow\_data\_write() API to encode the flow data structure into hardware format

- ncp\_vp\_task\_param\_decode\_func\_set Set task param decode function (used by ncp\_task\_recv() API of task I/O

module to decode the task parameters from the received task before sending them up to the application) for a

given engine sequence

- ncp\_vp\_task\_param\_encode\_func\_set Set task param encode function (used by ncp\_task\_send() and ncp\_task\_send\_segments() APIs) of task I/O module to encode the task parameters) for a given Virtual Pipeline instance

- ncp\_vp\_engine\_seq\_id\_get Get the engine sequence id given a Virtual Pipeline instance handle and the Engine Sequence name

- ncp\_vp\_flow\_data\_write Write a flow data entry for the given vpHdl, engineSeqld, and flowId

- ncp\_vp\_flow\_data\_read Read a flow data entry for the given vpHdl, engineSeqld, and flowId

## **Task Communication**

To pass information or data between engines, an Axxia device uses data structures called *tasks*. Tasks provide engines with the following types of information.

- Packet data

- Information on how to process the packet

- The next engine to receive the task

## **Messaging in Pipelines**

Engine sequence processing begins with the launching of a task by the first engine in the sequence, and ends with the last engine in the sequence consuming that task. Each task is typically associated with a packet, although you can have tasks without packets.

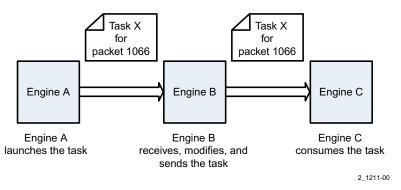

The following figure illustrates a simple engine sequence of three engines.

#### Figure 3 Engine Sequence Task Flow

The engine sequence task flow in the previous figure defines the following process.

- 1. Engine A, a start engine, creates and launches the new task, task X, to process packet number 1066.

- 2. Engine B, an intermediate engine, receives the task, reads its processing parameters, and optionally modifies the task and its packet. When Engine B completes processing, it sends the task to Engine C.

- 3. Engine C, an end engine, receives the task and consumes it.

When launching a task, some start engines can make decisions about task processing that include the following options.

- Launch a new task that continues processing the packet down another pipeline.

- Discard the packet and task.

- Perform any of the following programmed functions.

- Send out a different packet

- Send out multiple packets

- Generate an error.

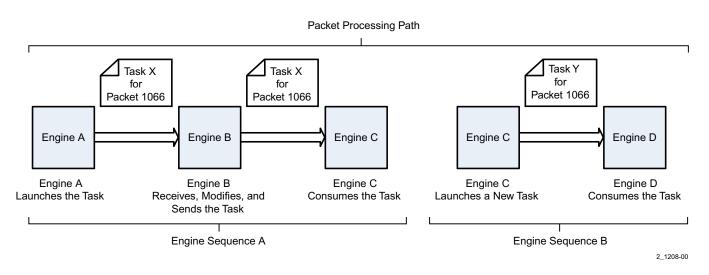

For example, to send the packet forward in another pipeline, the start engine creates and launches a new task for additional processing. The following figure shows the process.

#### Figure 4 Two Engine Sequences in a Processing Path

## Passing Parameters Using Tasks

As part of the task, each engine receives a set of input parameters and transmits a set of output parameters.

The following sources provide the parameters the tasks can pass.

- The start engine can generate the input parameters for any engines in the pipeline, and include them in the task.

- Intermediate engines can calculate input parameters as part of their processing, and add them to the task for a downstream engine in the engine sequence.

## **Task Management**

The Axxia architecture provides the following features for managing tasks.

- Task Queueing Each engine maintains queues for input tasks, called task receive queues, that have buffer management capabilities.

- Sending Backpressure Engines can send backpressure based on task buffer usage or other specific conditions.

- Mapping Task Priority Task priority is a value from 0-7 that is mapped to a receive queue. This mapping

determines the queues to which the tasks are delivered.

- Maintaining Task Order Tasks can optionally be created with a task order ID, a number used to ensure that an engine can process packets from a given flow that have the same task order ID in arrival order without restricting the relative ordering between packets of other flows which have different task order IDs. Engines that take advantage of task order ID will have taskOrdering as an input parameter shown in the ASE when building a pipeline that uses them.

- Load Balancing For accelerator engines consisting of multiple parallel engines, the tasks can be used for load balancing by distributing the tasks among the engines.

#### **Task Receive Queues**

Each engine maintains an address space in system memory for one or more task receive queues to store incoming tasks. The number of queues varies, depending on the following engine type.

MPP – The MPP engine has four task receive queues.

NCA – The NCA supports up to 12 task receive queues, six per core.

**EIOA** – The EIOA engine has two task receive queues for each port.

**MTM** – The MTM engine has four task receive queues, two task receive queues for unicast traffic and two for multicast traffic.

The task priority is a value from 0-7 that is mapped to a receive queue. This mapping determines the queues to which the tasks are delivered. The following sources can define a task's priority.

- The pipeline start engine. For example, the MPP defines the task priority as a parameter when it sends a new task.

- Flow data. The task priority is set by a value defined for a flow in a flow data table.

- The pipeline configuration.

You specify (in the ASE under Engines-<engine name>-TaskReceive) the mapping of the task priority to task receive queues for each engine. For example, with four task receive queues, you can assign one queue as the highest priority, and assign it tasks with priority 0 and 1. The next highest priority queue receives tasks with priority 2 and 3, and so on.

**NOTE** Priority 0 is special priority, that is, these tasks can not be dropped. It should be reserved for critical operations and not for regular packet processing.

You can configure the arbitration of the task receive queue servicing using the following scheduling algorithms.

- Weighted Round Robin Define weights for each task receive queue to define the servicing ratio between queues.

- Strict Priority The highest priority queue with traffic is always serviced.

- Rotating Servicing that attempts to strictly maintain servicing queues in a sequence, even if queues have previously been skipped because they were empty. For example, with four queues, if the current queue to be serviced is two, but queues two and three do not have any tasks to service, the fourth queue is serviced. On the next round servicing begins with the third queue, strictly maintaining the servicing sequence as if all queues always have traffic.

- Round Robin Round robin servicing begins servicing queues with the next queue in sequence after the

previously serviced queue. For example, with four queues, if the current queue to be serviced is two, but queues

two and three do not have any tasks to service, the fourth queue is serviced, then on the next round the first

queue is serviced, always following the last queue serviced.

#### Task Receive Queue Management

Task receive queues have thresholds levels that trigger actions. You can configure these thresholds and manage the buffers, based on queue occupancy (as number of tasks or as 256B memory blocks) and system buffer availability.

Task buffer management behavior is defined by setting the following attributes for the buffer size of each queue, per task priority.

Backpressure – Sets the buffer fill level that triggers a backpressure signal.

Applications can send backpressure messages to monitor the current occupancy of the task queues and signal the EIOA, MTM, MPP or CPU so they can react earlier. With the MPP and CPU the result of the backpressure signal is programmable; the EIOA can send PAUSE frames and in the MTM, backpressure signals can be mapped to queues and schedulers, based on the configuration or scripts.

- If the system configuration does not use the backpressure messages, packets are dropped based on the following discard schemes of the queue.

- Discard Random Sets the buffer fill size that triggers the Random Early Discard (RED) buffer management policy. The behavior of the algorithm is based on the RED slope value, and the relationship to the Discard All value.

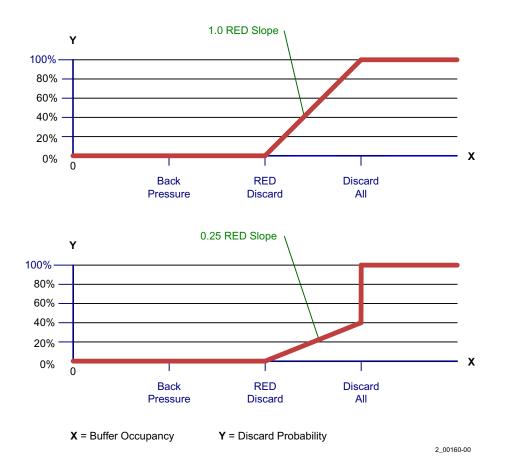

- RED Slope Defines the slope of a vector, from 0 to 1; with a larger slope value defining a more aggressive buffer protection policy. This slope is used to determine the discard probability of incoming tasks when the buffer size is in the range from Discard Random to Discard All. The vector is graphed as a buffer size (X axis value) that triggers the discard probability (Y axis value) based on the RED slope value. The formula is Discard Probability Percentage = Percentage of Buffer (Discard All Discard RED) x (RED Slope).

- Discard All Sets the buffer fill level that ends the RED algorithm and discards all new tasks.

**NOTE** Engines do not discard tasks with priority 0 when they violate receive queue thresholds. Priority 0 tasks are only discarded based on the system buffer availability threshold for this task receive queue, configured for the Memory Management Block.

When a new task is received, it is assigned to a queue depending on the task priority. Each queue belongs to a Threshold group. Each group has a set of thresholds and a RED slope defined for each task priority. Those values are compared to the buffer state to determine whether the new task is kept or discarded.

You define a set of these values for each task priority using Threshold Groups. Most engines have a single group; the EIOA has two, and the NCA has eight. For example, you can select one of the two defined priority thresholds groups for each port you configure for the EIOA, changing the buffer management policy per port.

The following figure shows two similar configurations. The first example uses a 1.0 RED slope value and the second example uses a 0.25 RED slope value.

#### Figure 5 Sample RED Slope Discard Probability Examples

The higher 1.0 RED slope value has the more aggressive buffer protection behavior. Similarly, the maximum discard probability for a given slope is equal to the slope value multiplied by one hundred.

Use the ASE to configure task priority assignments to task queues, task queue scheduling arbitration, and the backpressure, discard random, and discard all thresholds for each task priority.

## **Maintaining Task Order**

Typically, most engines keep packets in order as they process them by maintaining them in unique flows. For some packet flows, it is important to process packets in order in accelerator engines that employ multiple parallel engines. For example, the Deep Packet Inspection (DPI) engine has multiple internal threads for searching. If you are using the DPI engine for cross-packet searches, you must ensure that, as a flow is processed by the DPI engine, the threads do not process different packets of the flow out of order.

To provide this capability, the task includes a field for task ordering called the Task Order ID determined by the application software. This field contains a compressed version of the flow ID. This 12-bit value ensures that, on engines with multiple logical task receive queues, if tasks are arriving concurrently with the same Task Order ID and the same task priority, they are assigned to the same subengine, to maintain their order.

For example, consider a high priority task with a Task Order ID of 6 arrives and is assigned to subengine 0. High priority tasks with the same Task Order ID are dynamically assigned to subengine 0. This is irrespective of the configured subengine assignment algorithm, such as load balancing. If a task with an Order ID of 6 arrives, and there are no other tasks in the flow with the same ID, the configured queue algorithm is used to assign the task to a queue. In this case, the task is assigned to subengine 1.

Additionally, unlike other tasks, those tasks with Task Order IDs, or ordered tasks, are treated as if they have not been removed from the task receive queue until the processing of that task is complete. This ensures that while the engine is processing an ordered task, a task that arrives with the same priority and Task Order ID is not assigned to a different queue.

## Load Balancing using Tasks

Tasks can be used for load balancing for engines with built-in load balancing capabilities. These accelerator engines have multiple parallel- processing engines that are independently assigned tasks using the task receive queues.

The Axxia architecture has the following engines with built-in load balancing processing.

- DPI

- SPP

- Configure the NCA to provide multiple processors for pipeline processing

While the MPP has multiple parallel engines, tasks are balanced using task receive queues. Four task queues are used to prioritize traffic entering the MPP engine. Load balancing uses high and low priority logical queues and tracks the number of tasks being processed by that resource.

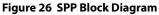

You can configure task load balancing to work in one of two modes.

- Processing engine Engine uses high and low priority queues as a single resource. New tasks are given to the processing engine with the lowest load in both high and low priority queues. This mode tends to provide a *more even distribution* to the overall task load, but may not provide enough resources to high priority tasks.

- Priority High priority tasks are given to the high priority task queue with the lowest load, and low priority tasks are given to the low priority queue with the lowest load, without regard to processing engine. This mode provides more resources to high priority tasks, but may not provide an even distribution to the overall task load.

The NCA does not use the task priority field for mapping tasks to queues. Priority with respect to the NCA queues is determined by the rate at which each queue is serviced by the software.

## **Flow Parameters**

To define a specific set of processing parameters for each processing flow in a pipeline you can define a flow table. You can use application software to create the flow (associated RTE APIs are briefly mentioned later in this chapter). In the table, you can use a programmable flow ID as an index to a set of parameter values that are organized as a flow table entry. The start engine for the pipeline loads the flow table values into the task. Thus, if the flow table is updated, any tasks that have already been launched will continue to use the original information that existed at the time they were launched.

The constant pipeline parameter values you define at configuration are stored in the engine's local template memory (which is not otherwise visible to application software), and the template is indexed by the task.

Use the ASE to manipulate the set of engines in an associated engine sequence. The ASE can determine what engines send the output parameters and receive the input parameters on an octet boundary with an octet-level granularity.

## Backpressure

This section introduces the concept of backpressure.

## **Backpressure Signals**

To control congestion and to optimize the use of resources, every engine can send backpressure signals. These are based on task receive queue buffer thresholds or specific conditions, such as port backpressure or other programmable conditions.

Backpressure signals can generate messages to turn backpressure on or off. To avoid excessive signaling when a buffer size hovers around the backpressure threshold and backpressure is asserted, engines use an ASE-configurable attribute (hysteresis). This delays sending backpressure messages to turn off backpressure until the buffer occupancy reaches a low enough value.

Although all engines can send backpressure signals, only four engines can receive the signals.

- NCA Makes the backpressure signal status available to software

- MPP Makes the backpressure signal status available to software

- EIOA Backpressure messages can trigger signalling Ethernet backpressure using PAUSE frames

- MTM Backpressures queues and schedulers

The CPU and MPP engines permit you to map the backpressure state of different queues using up to 32 flags each. The Axxia device makes the status of these flags available to an FPL program running in the MPP, or to a program running on the CPU. This availability is through variables defined in the ASE generated header files.

Engines can make decisions and take action depending on the backpressure status of a queue or set of queues. For example.

- The ingress EIOA can read port-based backpressure signals to control the reception of new packets.

- The MTM can read backpressure signals to control packet scheduling queues and schedulers. A backpressured queue or scheduler cannot transmit traffic.

You can configure the backpressure behavior in the following ways.

- Assign a single backpressure source to a single destination.

- Assign a single backpressure source to multiple destinations.

- Assign multiple backpressure signal sources to a single destination.

- Assign multiple backpressure signal sources to a multiple destinations.

## Namespaces

A namespace is a region of memory that contains one or more engine tables. Engine tables are data structures that some accelerator engines access and maintain.

The Axxia device provides a uniform way of creating and accessing engine tables. Namespaces provide an optimal way to organize and assign the pool of system memory for engine tables, without requiring you to perform detailed memory mapping.

Logically, the software partitions the memory into namespaces and engine tables that are indexed by a 24-bit value. The maximum number of engine table entries in all namespaces that you can allocate is 16M, due to the 24-bit index.

The engine tables hold specific data structures required by individual accelerator engines. Optionally, a namespace can contain more than one engine table.

You configure the maximum number of entries for namespaces and the entry sizes for the engine tables through the ASE. Entries can be added or deleted dynamically.

## **Engine Tables**

The following list describes the different types of engine tables that you can configure within namespaces.

- Scheduling queues, schedulers, and scheduling levels (MTM)

- Shared scheduling parameters (MTM)

- Stream Editor parameters (SED)

- Deep packet inspection contexts (DPI)

- Packet Assembly Block reassemblies (PAB)

- Stateful classification, policing and statistics tables (MPP state engine)

- Security Association information (SPP)

- Cancellable timer information (TMGR)

You can define these structures in your hardware configuration file through the ASE. You can populate them dynamically as needed during processing.

## **Namespace Configuration**

Use the ASE — under Namespaces > Namespace (*name*) — to configure each namespace. To configure a namespace, define the number of entries. This value is the maximum number of entries in the namespace, and by extension the maximum number of entries for all engine tables within the namespace. For each engine table, you define an entry size (width).

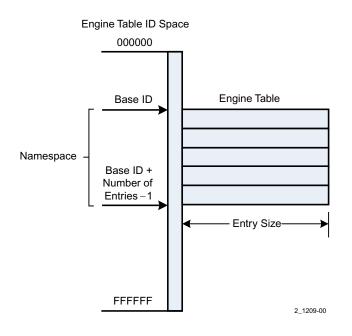

For example, to perform IP Reassembly with a requirement to support 1000 simultaneous reassemblies, configure a namespace with 1000 entries and a PABReassemblies engine table within that namespace. The ID of the first entry in the namespace is called the base ID. The ASE can automatically assign the base ID values for all namespaces. The figure below illustrates the base ID and number of entries for a namespace and the entry size for an engine table.

Figure 6 Base ID for Engine Namespace Table

The Axxia architecture uses namespaces to support the following features.

- Engine tables can have different entry sizes. This improves memory usage because you do not have to define the

maximum entry size for the engine.

- By configuring multiple engine tables in the same namespace, the namespace reserves a range of IDs for use by multiple engines. In this case, the same ID values can be used to index the corresponding entries in multiple engine tables. This reduces the number of entry ID lookups required and the number of parameters passed between the engines. For example, the MPP and the PAB could share the same range of IDs for a set of packet flows.

- The architecture enables entries from multiple engine tables within a namespace to alternate within memory. This memory layout is called *striping*. Striping allows entries from the different engine tables to be placed in the same cache line. This layout can increase both locality of the memory accesses and performance of some applications. The system cache has a line size of 256 bytes.

- Atomic write operations for engine table entries allow the software to update the engine table entries at runtime, without risking a race condition. For example, the atomic write capability enables updating a scheduling structure while the MTM is using it to schedule traffic.

#### **Engine Table Characteristics**

Each engine table has specific features to support its associated accelerator engine. See the engine-specific chapters in this document for additional details specific to each engine.

#### MPP State Engine

Use an engine table for the MPP State Engine to set up entries that serve as storage space for C-NP scripts that run in the State Engine compute engine. This storage space is typically used to track state such as counters, statistics, reassembly status, or policing results. Entry size can be up to 256 bytes. An individual entry can store multiple items adjacent to each other within the entry. The FPL code uses a 24-bit index and an 8-bit offset to access the engine table.

#### PAB Engine

The Packet Assembly Block engine table reserves packet reassembly memory space. Each reassembly requires an entry of either 128 bytes or 256 bytes. If you use timers for reassembly, you must use the 256-byte entry size. If timers are not used for reassembly, use the 128-byte entry size.

#### SED Engine

Although the Stream Editor engine table is not required for SED processing, using it provides additional editing flexibility and features. The SED engine table can provide additional parameter bytes, alternative parameter values, and up to 240 bytes of packet prepended data.

You can define one of the following engine tables for different types of SED parameters.

- Direct Parameters Support 16 or 32 bytes of programmable parameters per entry. These parameters are made available to the SED C-NP script.

- Indirect Parameters Support up to 256 bytes of parameters in a fixed structure. This includes any data to be

prepended to the packet. This can also include SED commands that indicate, for example, which script to

execute or how to perform fragmentation. In addition, up to 32 bytes of indirect parameters can be made

available to the SED script.

#### TMGR Engine

The engine table for the TMGR is required *only* if you are using the TMGR directly in a pipeline engine sequence to support *cancellable* timers. Only the CPU and MPP engines can be used as start or end engines for the TMGR in a pipeline engine sequence.

When timers are used indirectly in the MPP, for example, in a hash table entry, or by the PAB or MTM, an engine table for the TMGR is not necessary.

#### MTM Engine

The MTM employs the following types of namespace and engine table entities.

- MTM Scheduler Level A special namespace used to define a level of scheduling hierarchy. Depending on the level, you can add schedulers to it. The special namespace stores the schedulers as fixed format entries.

- MTM Scheduler Schedulers are added as entries in the scheduler level namespace. Their configuration information is stored in a fixed 64-byte format.

- MTM Queue Queues do not belong to the MTM scheduler level namespace. They must be added as an

engine table in a different namespace. Queue configuration information is stored in a fixed 64-byte format

within the engine table.

- MTM Shared Parameters Shared parameters do not belong to the MTM scheduler level namespace. This

optional engine table defines parameters used by the Buffer Traffic Manager and Traffic Shaper compute

engines of the MTM. The entry size is fixed at 32 bytes.

#### DPI Engine

The DPI engine can use large or small memory buffers, called *contexts*, for its pattern matching functions. Small contexts are defined as equal to or less than 256 bytes. The DPI engine automatically requests large context memory when needed from the Memory Management Block (MMB). For small context storage space, the DPI Contexts engine table must be defined with an entry size of either 32, 64, 128, or 256 bytes.

SPP Engine

The Security Protocol Processor engine requires storage space to store information and status for each secure connection. This space is called a security *context* (or a security association). You can configure the entry size up to 256 bytes, which depends on the protocol used, such as IPsec.

## Namespaces with More than One Engine Table

The Axxia architecture defines namespaces that specify a range of IDs for a single engine or for multiple engines to access. This capability enables the effective creation of parallel engine tables with identical ID ranges so common traffic flows can use the same ID values in different engines.

For example, the MPP State Engine and PAB can use parallel engine tables in the same namespace. When reassembling packets, the ID that the State Engine uses to refer to the packet reassembly can also be used by the PAB. Typically, accelerator engines share data using tasks. If two or more engine tables reside in the same namespace, you can configure the engine tables so that multiple engines can share data by reading and writing engine table entries.

## **Engine Table Entry Size and Memory Usage**

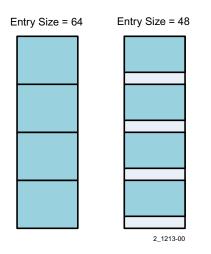

One of the hardware requirements for the entries in engine tables is memory alignment. Each entry must start on a boundary whose value is a power of 2.

For a namespace with a single engine table, this requirement implies that an entry always occupies a memory chunk that is a power of 2. For example, consider the following figure. If the MPPStateEngine engine table has an entry size of 64 and the size is changed so that the entry size is 48, the resulting engine table takes up the same amount of memory, with 16 bytes wasted per entry. To reduce the memory footprint of this engine table, you must further reduce the entry size to 32 bytes. The most memory-efficient entry sizes are power of 2 sizes.

#### Figure 7 Entry Size Comparison

Even though reducing entry size from 64 bytes to 48 bytes does not save any memory, it does save memory bandwidth. This bandwidth saving occurs because less data needs to be transferred between the accelerator engine and the memory subsystem. The savings can result in marginal performance improvements.

If a namespace has multiple engine tables that are not striped, the same memory efficiency issues apply to each engine table in the namespace. The power of 2 entry sizes are the most memory efficient.

Striped engine tables provide the only case where entries without power of 2 entry sizes can save memory. For example, when you stripe a SED engine table with an entry size of 16 bytes with an engine table for the MPP State Engine with an entry size of 48 bytes, the result fits into a 64-byte cache line. Striping the engine tables together is more memory efficient than leaving them non-striped.

## Managing Namespaces and Engine Tables from FPL Software or Using the RTE

For most system designs, the namespaces and engine tables are created through the ASE, reserving memory for table data. The engine tables are then populated and managed at run time, during operation.

After an engine table is defined and the software application starts adding and removing entries, a mechanism is needed to keep track of the entry IDs. For example, when the software sets up a new application flow, it must add an engine table entry. To add the entry it must find a free entry, mark it as in-use and use it to set up the flow. The LSI hardware and software provide two ways to manage entries for a namespace: from an FPL program or through RTE APIs.

#### Using the RTE APIs for Engine Table Management

The following list shows the RTE APIs for engine table management.

- ncp\_rsrc\_create Create a resource enumeration object

- ncp\_rsrc\_destroy Destroy a resource enumeration object

- ncp\_rsrc\_find Find the named object

- ncp\_rsrc\_allocate Allocate contiguous ID(s)

- ncp\_rsrc\_allocate\_fixed Allocate contiguous ID(s) starting at the given ID

- ncp\_rsrc\_free Release previously allocated ID(s)

- ncp\_rsrc\_isset Check whether the ID has already been reserved

- ncp\_rsrc\_query Query the attributes for a given ID

- ncp\_rsrc\_dump Dump a listing of the resources of a specified type or types to standard output (stdout)

**NOTE** These APIs are generic, that is, they can manage a set of entry IDs for any purpose, including but not limited to engine table ID management.

## Engine Table Management using an FPL Program

The fplManaged attribute of a namespace element in the ASE designates whether the engine tables in a given namespace are managed by an FPL program or through RTE APIs. The following restrictions apply.

- An FPL program can manage a maximum number of 16 engine tables.

- The FPL managed engine tables cannot have entries defined statically in the ASE. They should not be accessed through RTE APIs.

- The number of entries in an FPL-managed engine table must be a multiple of 20 and cannot exceed 2<sup>20</sup> (approximately 1M).

## Sharing Data Between Engine Tables

The Axxia architecture uses tasks as the most efficient way for engines in an engine sequence to communicate with each other. This includes sending data from one engine to another. Task communication associates data with specific packets and automatically maintains data and control information integrity.

You can also configure engine tables within a single namespace to share data with each other. This capability is only available for specific accelerator engines.

Sharing data allows entry modifications done by one engine to be visible to another engine. However, sharing engine table entries has a risk. If an entry contains control information, such as memory block addresses obtained from the MMB, the possibility of error exists. If you corrupt the control information, you can lock up the device or corrupt packet data.

To avoid potential problems, only the following engine tables support data sharing.

- MPP State Engine table

- MTM Shared Parameters

- SED Direct Parameters

SED Indirect parameter entries contain control information, so they do not support sharing.

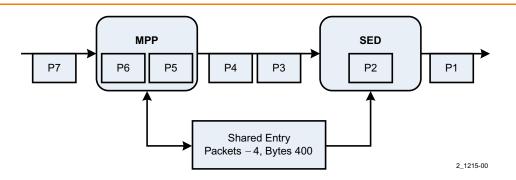

Because a system design normally has multiple packets in flight, data sharing can work differently from what is expected in a single-threaded application, as shown in the following example.

- Assume the pipeline is MPP->SED-> (other engines). An engine table for the MPP State Engine shares data with a SED Direct Parameters engine table.

- The MPP maintains byte and packet counts, while the SED reads and uses the counts.

- Seven packets are sent into this pipeline engine sequence, P1-P7, 100 bytes each.

The following figure shows an example of the shared engine table entry latency.

#### Figure 8 Shared Data Table Entry Latency

Consider what happens when the SED accesses packet P2. If the system worked with one packet at a time, the values would be packets=2, bytes=200. However, by the time P2 gets to the SED, the subsequent packets, P3 and P4, have been completed by the MPP and are waiting in the SED's task receive queue. This means the SED reads the values from the shared entry as packets=4, bytes=400. In general, when engine tables share data, it is difficult to predict the packet and byte values the downstream engine reads. In this example, for the P2 values read by SED the only prediction that can be made is that packets  $\geq$  2 and bytes  $\geq$  200.

## Using the readThrough and writeThrough Modes in Sharing

Because there are readThrough and writeThrough flags for every engine table, setting them for shared tables does not affect the performance of other engine tables. These attributes are configured per engine table and their values are transferred to the hardware when the base IDs are assigned.

The readThrough and writeThrough attributes place additional constraints on base ID assignment. For example, the area of address space used for engine tables is a factor. The ASE cannot define a namespace that contains an engine table for the MPP State Engine with writeThrough set to true in the same area of internal memory as a namespace that contains an engine soft and engine table for the MPP State Engine with writeThrough set to true in the same area of internal memory as a namespace that contains an engine table.

**NOTE** In general, do not enable the readThrough or writeThrough attributes unless you share data between engine tables, because these attributes affect performance.

For the previous example with an MPP->SED pipeline, you must set writeThrough to true for the MPPStateEngine engine table. No readThrough setting is required for the SED Direct Parameters table because the SED does not use the L1 cache (caches namespace table contents between system cache and each engine).

If you have a pipeline engine sequence that includes (other engines) ->MTM->MPP and you need to share the data between the MTM Shared Parameters and the MPP State Engine engine tables, set writeThrough to true for the MTM Shared Parameters and readThrough to true for the MPP State Engine.

## Using the Level 1 Cache

For a SED Direct Parameters engine table, there is no Level 1 cache. The SED reads the complete engine table entry for every packet.

For MTM Shared Parameters, the MTM engine uses Level 1 cache. When readThrough is set to true, the merge is done on 16-byte granularity.

The MPP State Engine has the following Level 1 caches.

- Stat (ALU) cache. It has 16-byte entries and is responsible for built in functions such as selncrement32 and seWrite32, that are invoked from the FPL code.

- State Engine script cache. It has 64-byte entries and is used for caching the contents of param\_block1 and param\_block2.

The readThrough and writeThrough flags set for the MPP State Engine engine table apply to both L1 caches simultaneously. When readThrough is set to true, the merge is done on a byte granularity for the first 16 bytes of the cache entry size and on a 16-byte granularity for the remaining 48 bytes of the State Engine script cache.

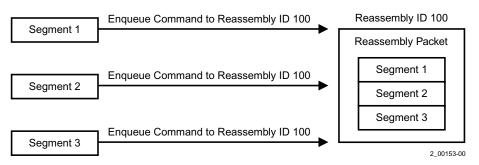

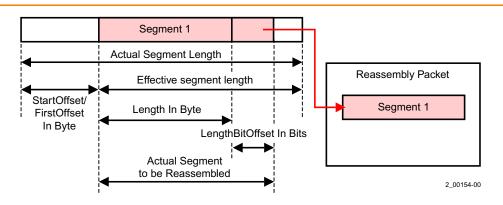

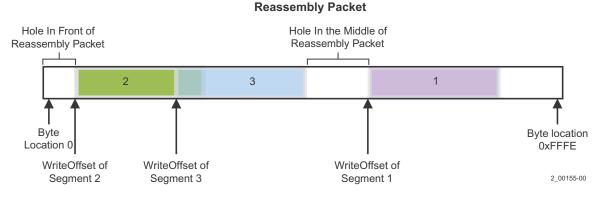

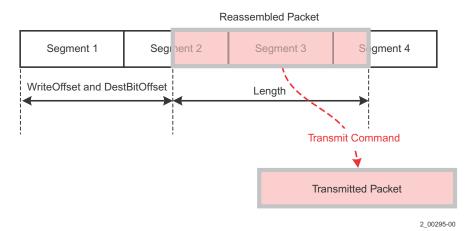

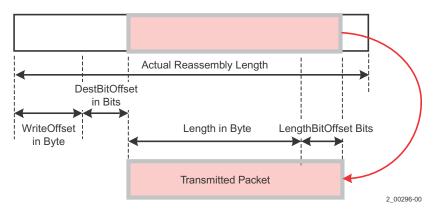

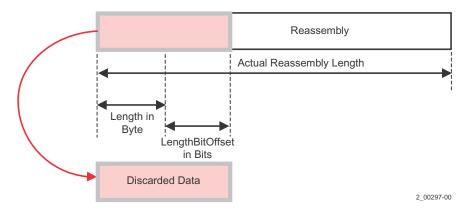

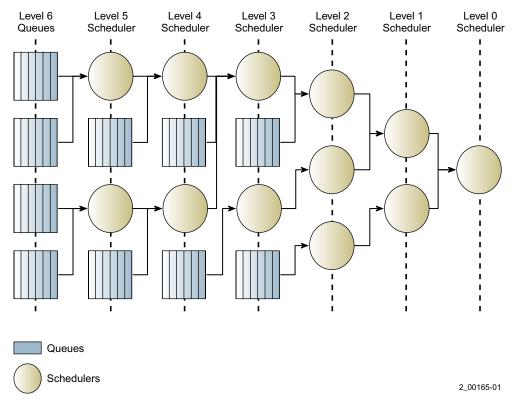

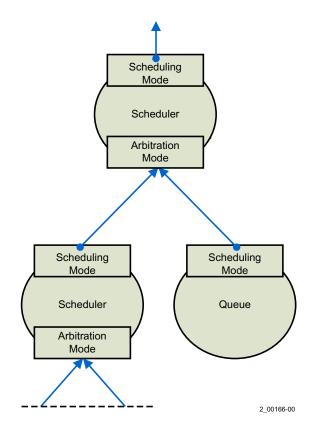

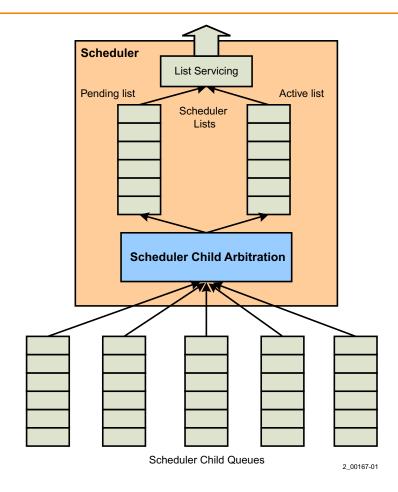

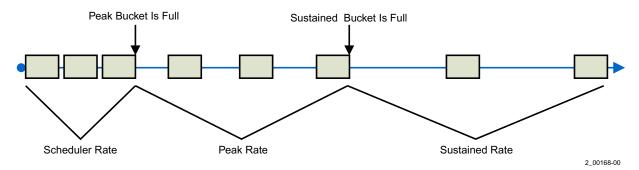

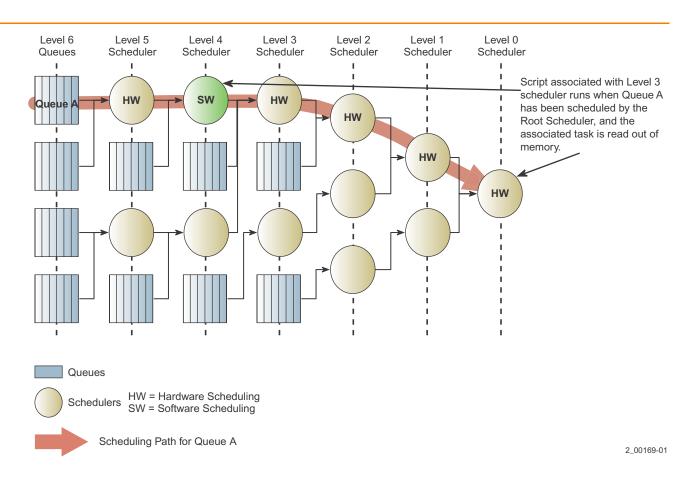

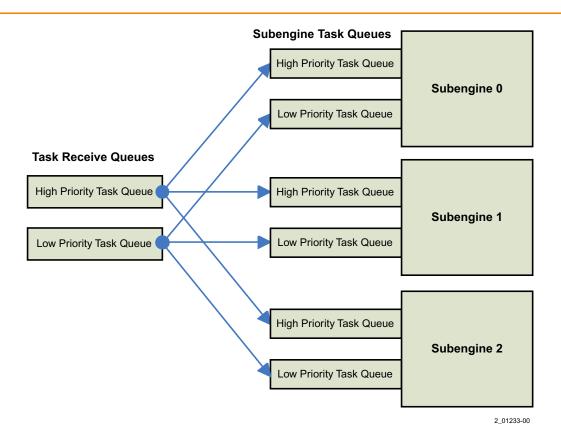

#### MPP State Engine Data Sharing